#### About this Manual

We've added this manual to the Agilent website in an effort to help you support your product. This manual is the best copy we could find; it may be incomplete or contain dated information. If we find a more recent copy in the future, we will add it to the Agilent website.

## **Support for Your Product**

Agilent no longer sells or supports this product. Our service centers may be able to perform calibration if no repair parts are needed, but no other support from Agilent is available. You will find any other available product information on the Agilent Test & Measurement website, <a href="https://www.tm.agilent.com">www.tm.agilent.com</a>.

#### **HP References in this Manual**

This manual may contain references to HP or Hewlett-Packard. Please note that Hewlett-Packard's former test and measurement, semiconductor products and chemical analysis businesses are now part of Agilent Technologies. We have made no changes to this manual copy. In other documentation, to reduce potential confusion, the only change to product numbers and names has been in the company name prefix: where a product number/name was HP XXXX the current name/number is now Agilent XXXX. For example, model number HP8648A is now model number Agilent 8648A.

## **SERVICE MANUAL**

## HP 16510B 35 MHz State/ 100 MHz Timing Card

© COPYRIGHT HEWLETT-PACKARD COMPANY/COLORADO DIVISION 1989 1900 GARDEN OF THE GODS ROAD, COLORADO SPRINGS, COLORADO U.S.A.

ALL RIGHTS RESERVED

Manual Part No. 16510-90912 PRINTED: JUNE 1989

#### **TABLE OF CONTENTS**

SECTION I **General Information** Modules Covered By This Manual ...... 1-1 1-2. 1-3. 1-4. 1-5. Accessories Available 1-2 1-7. Specifications 1-2 SECTION II Installation 2-3. Power Requirements 2-1 2-4. 2-5. 2-6. 2-7. 2-8. SECTION III **Performance Tests** Introduction 3-1 3-3. 3-4 Performance Test Interval 3-1 3-5. 3-6. 3-7.

## SECTION IV Adjustments

| 4-1.<br>4-2.<br>4-3.<br>4-4.<br>4-5.<br>4-6.<br>4-7. | Introduction Calibration Interval Safety Requirements Recommended Test Equipment Extender Board Installation Instrument Warmup Adjustment And Calibration Check | 4-1<br>4-1<br>4-1<br>4-1<br>4-4 |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| SECTION Replace                                      | N V<br>able Parts                                                                                                                                               |                                 |

| 5-1.                                                 | Introduction                                                                                                                                                    | 5-1                             |

| 5-2.                                                 | Abbreviations                                                                                                                                                   |                                 |

| 5-3.                                                 | Replaceable Parts List                                                                                                                                          |                                 |

| 5-4.                                                 | Ordering Information                                                                                                                                            |                                 |

| 5-5.                                                 | Exchange Assemblies                                                                                                                                             |                                 |

| 5-6.                                                 | Direct Mail Order System                                                                                                                                        | 5-2                             |

| SECTION Service                                      | N VI                                                                                                                                                            |                                 |

| 6-1.                                                 | Introduction                                                                                                                                                    | 6-1                             |

| 6-2.                                                 | Safety Requirements                                                                                                                                             | 6-1                             |

| 6-3.                                                 | Recommended Test Equipment                                                                                                                                      | 6-1                             |

| 6-4.                                                 | Module Block Diagram And Theory Of Operation                                                                                                                    |                                 |

| 6-5.                                                 | Self Tests                                                                                                                                                      |                                 |

| 6-6.                                                 | Troubleshooting Auxiliary Power                                                                                                                                 |                                 |

| 6-6.                                                 | Troubleshooting The HP 16510B                                                                                                                                   |                                 |

| 6-7.                                                 | Module Replacement                                                                                                                                              |                                 |

| 6-8.                                                 | Probe Assembly Replacement                                                                                                                                      | 6-17                            |

## **LIST OF TABLES**

| TITLE                                    | PAGE                    |

|------------------------------------------|-------------------------|

| IP 16510B Specifications                 | 1-3                     |

| IP 16510B Operating Characteristics      | 1-4                     |

| ecommended Test Equipment                | 1-9                     |

| erformance Test Record                   | 3-33                    |

| Reference Designations and Abbreviations | 5-3                     |

| Leplaceable Parts List                   | 5-5                     |

|                                          |                         |

|                                          | P 16510B Specifications |

## **LIST OF FIGURES**

| FIGURE | TITLE                                    | PAGE |

|--------|------------------------------------------|------|

| 2-1.   | Endpate Overlap                          | 2-2  |

| 2-2.   | Cable Position                           | 2-3  |

| 2-3.   | Endplate Overlap                         | 2-3  |

| 3-1.   | Test Connector                           |      |

| 3-2.   | Equipment Setup For Test 1               |      |

| 3-3.   | Pulse Generator Waveform For Test 1      | 3-3  |

| 3-4.   | Configuration Screen                     |      |

| 3-5.   | Format Screen For Pod 1 and J Clock Test | 3-4  |

| 3-6.   | Format Screen / Clock Assignment         |      |

| 3-7.   | Format Screen / Bit Assignment           |      |

| 3-8.   | Trace Screen                             |      |

| 3-9.   | Listing Screen                           |      |

|        | Switching To Next Probe Cable            |      |

|        | Equipment Setup For Test 2               |      |

|        | Pulse Generator Waveform For Test 2      |      |

| 3-13.  | Format Screen                            | 3-8  |

|        | Trace Screen                             |      |

|        | Listing Screen                           |      |

|        | Equipment Setup For Test 3               |      |

| _      | Pulse Generator Waveform For Test 3      | _    |

|        | Listing Screen                           |      |

|        | Equipment Setup For Test 4               |      |

|        | Pulse Generator Waveform For Test 4      |      |

|        | Listing Screen                           |      |

|        | Equipment Setup For Test 5               |      |

|        | Pulse Generator Waveform For Test 5      |      |

| 3-24.  | Listing Screen                           | 3-18 |

|        |                                          |      |

## **LIST OF FIGURES**

| FIGURE | TITLE                                    | PAGE   |

|--------|------------------------------------------|--------|

| 3-25.  | Equipment Setup For Test 6               | . 3-19 |

| 3-26.  | Pulse Generator Waveform For Test 6      | . 3-20 |

| 3-27.  | Format Screen                            | . 3-21 |

| 3-28.  | Listing Screen                           | . 3-21 |

| 3-29.  | Equipment Setup For Test 7               | . 3-22 |

| 3-30.  | Pulse Generator Waveform For Test 7      | . 3-23 |

| 3-31.  | Format Screen                            | . 3-24 |

| 3-32.  | Listing Screen                           | . 3-24 |

| 3-33.  | Equipment Setup For Glitch Test          | . 3-25 |

| 3-34.  | Pulse Generator Waveform For Glitch Test | . 3-26 |

| 3-35.  | Configuration Screen                     | . 3-26 |

| 3-36.  | Format Screen                            | . 3-27 |

| 3-37.  | Trace Screen                             | . 3-27 |

| 3-38.  | Listing Screen                           |        |

| 3-39.  | Equipment Setup For Threshold Accuracy   | . 3-29 |

| 3-40.  | Format Screen                            | . 3-30 |

| 3-41.  |                                          |        |

|        | Waveform Screen                          |        |

| 3-43.  | Waveform Screen                          | . 3-32 |

| 4-1.   | Endplate Overlap                         | . 4-2  |

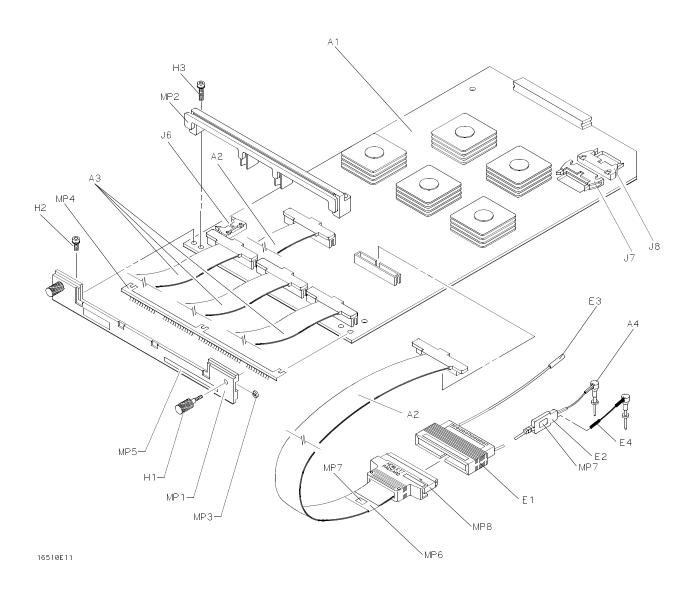

| 4-2.   | Extender Board And Module                | . 4-3  |

| 4-3.   | Adjustment Pot Location                  | . 4-4  |

| 4-4.   | Startup Screen                           |        |

| 4-5.   | Pod Threshold Field                      | . 4-5  |

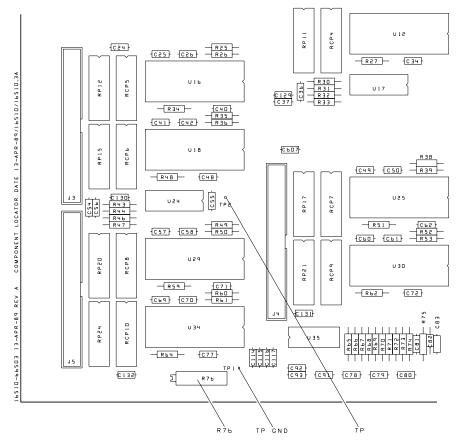

| 5-1.   | Parts Identification                     | . 5-4  |

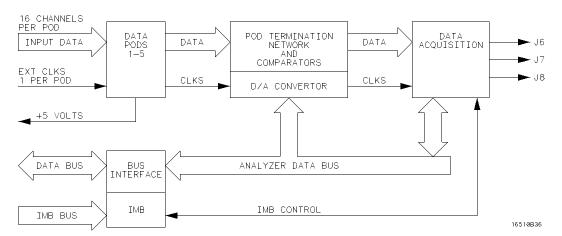

| 6-1.   | HP 16510B Module Block Diagram           | . 6-1  |

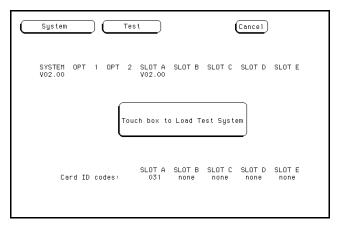

| 6-2.   | Startup Screen                           | . 6-3  |

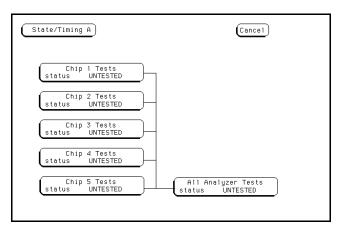

| 6-3.   | Load Test System                         | . 6-4  |

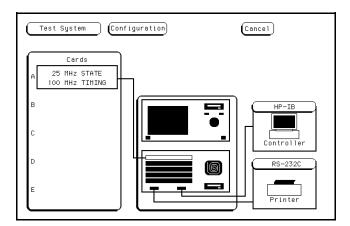

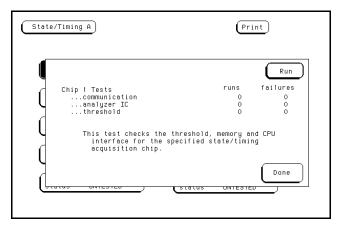

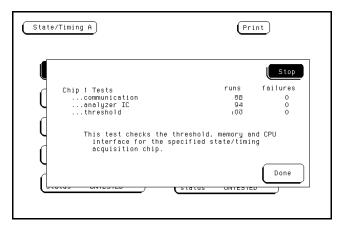

| 6-4.   | Test System Screen                       |        |

| 6-5.   | Main Test Menu                           |        |

| 6-6.   | Chip 1 Test Run Screen                   |        |

| 6-7.   | Stop Field                               |        |

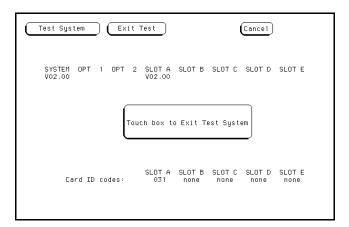

| 6-8.   | Exit Test System                         |        |

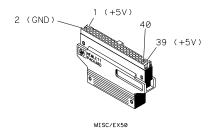

| 6-9.   | Power And Ground                         |        |

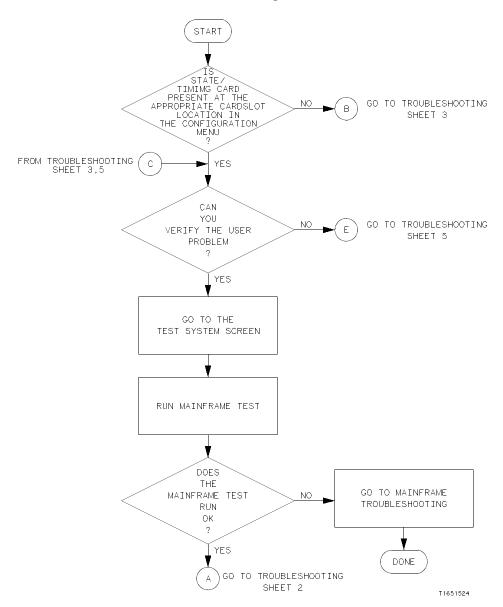

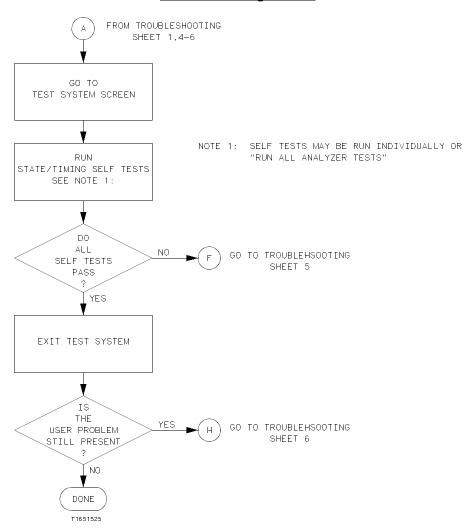

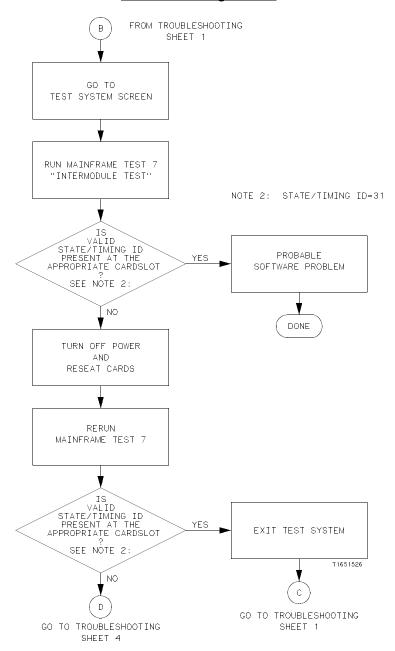

|        | Troubleshooting Flowchart                |        |

|        | Endplate Overlap                         |        |

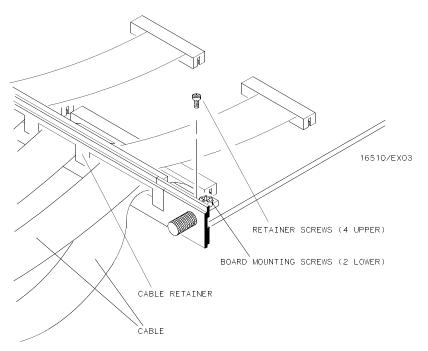

|        | Cable Position                           |        |

|        | Ensplate Overlap                         |        |

|        | Endplate Overlap                         |        |

|        | Card On Antistatic Mat                   |        |

|        | Retainer And Screws                      |        |

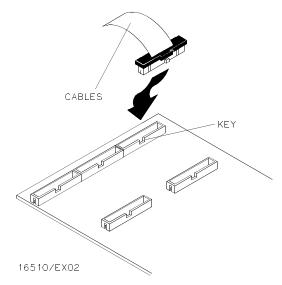

| 6-17.  | Card Connectors                          | . 6-19 |

## **TABLE OF CONTENTS**

#### **General Information**

| 1-1. | Introduction               | 1-1 |

|------|----------------------------|-----|

| 1-2. | Modules Covered By Manual  | 1-1 |

| 1-3. | Safety Requirements        | 1-1 |

|      | Product Description        |     |

|      | Accessories Supplied       |     |

| 1-6. | Accessories Available      | 1-2 |

| 1-7. | Specifications             | 1-2 |

|      | Operating Characteristics  |     |

|      | Recommended Test Equipment |     |

# SECTION I General Information

#### 1-1. Introduction

This service manual contains information for testing, adjusting, and servicing the HP 16510B State/Timing Module. Also included are installation procedures and a list of recommended test equipment. This manual is divided into six sections as follows:

- I General Information

- II Installation

- III Performance Tests

- IV Adjustments

- V- Replaceable Parts

- VI Service

Information for operating, programming, and interfacing the HP 16510B State/Timing Module is contained in the HP 16510B State/Timing Operating and Programming Manual supplied with each module.

The General Information Section includes safety requirements, a product description, and a list of accessories supplied and of accessories available. Also included are tables listing specifications and operating characteristics, and a list of recommended test equipment.

To complete the service documentation for your system, place this service manual in the 3-ring binder with your Logic Analysis System Service Manual.

## 1-2. Modules Covered by Manual

The information covered in this manual is for the HP 16510B State/Timing Module.

#### 1-3. Safety Requirements

Specific warnings, cautions, and instructions are placed wherever applicable throughout the manual. These must be observed during all phases of operation, service, and repair of the module. Failure to comply with them violates safety standards of design, manufacture, and intended use of this module. Hewlett-Packard assumes no liability for the failure of the customer to comply with these safety requirements.

#### 1-4. Product Description

The HP 16510B State/Timing Module is an 80 channel, 35 MHz state, 100 MHz timing logic analyzer. It can be configured as two independent state analyzers or one state and one timing analyzer. Some of the main features are:

- Simultaneous state/state, or simultaneous state/timing analysis.

- Time interval; number of states; pattern search; minimum, maximum, and average time interval statistics.

- Uses transitional timing to store data only when there is a transition.

- 5 clock inputs, 4 clock qualifiers, storage qualification, time and number of state tagging, and prestore.

- · Small lightweight probing.

- Configurable to 160 channels wide (HP 16511B).

#### 1-5. Accessories Supplied

The following accessories are supplied with the HP 16510B State/Timing module. Quantity one unless shown otherwise.

- Operating and Programming Manual Set

- Service Manual

- 16 Channel Lead Sets, grey tip (HP 01650-61608) Qty 5

- 16 Channel Probe Cable (HP 16510-61602) Qty 2

- 16 Channel Probe Cable (HP 16510-61601) Qty 3

- Grabbers (Set of 20)

(HP 5959-0288) Qty 5 sets

- Probe Cable ID Clip (HP 16500-41201) Qty 5

- Probe and Cable Numbering Labels (01650-94303)

- Cable Numbering Labels (16500-94303)

- Operating System Disk

#### 1-6. Accessories Available

Termination adapter (HP 01650-63201)

#### 1-7. Specifications

Module specifications are listed in table 1-1. These specifications are the performance standards against which the module is tested.

#### 1-8. Operating Characteristics

Table 1-2 is a listing of the module operating characteristics. The operating characteristics are not specifications, but are the typical operating characteristics included as additional information for the user.

## 1-9. Recommended Test Equipment

Equipment required to test and maintain the HP 16510B State/Timing Module is listed in table 1-3. Other equipment may be substituted if it meets or exceeds the critical specifications listed in the table.

#### Table 1-1. HP 16510B Specifications

#### **HP 16510B SPECIFICATIONS**

#### **Probes**

Minimum Swing: 600 mV peak-to-peak.

Threshold Accuracy: Voltage Range Accuracy

-2.0V to +2.0V  $\pm 150 \text{ mV}$

-9.9V to -2.1V ±300 mV

+2.1V to +9.9V  $\pm 300$  mV

#### **State Mode**

#### **Clock Repetition Rate:**

Single phase is 35 MHz maximum. With time or state counting, minimum time between states is 60 ns. Both mixed and demultiplexed clocking use master-slave clock timing; master clock must follow slave clock by at least 10 ns and precede the next slave clock by >50 ns.

Clock Pulse Width: ≥10 ns at threshold.

**Setup Time:** Data must be present prior to clock transition,  $\geq 10$  ns.

**Hold Time:**

Data must be present after rising clock transition on all pods; 0 ns.

Data must be present after falling clock transition on pods 1,3 and 5; 0 ns.

Data must be present after falling clock transition on pods 2 and 4; 1 ns.

#### **Timing Mode**

Minimum Detectable Glitch: 5 ns wide at the threshold.

#### **HP 16510B OPERATING CHARACTERISTICS**

#### **Probes**

**Input RC:** 100 K $\Omega$  ±2% shunted by approximately 8 pF at the probe tip.

TTL Threshold Preset: +1.6 volts.

ECL Threshold Preset: -1.3 volts.

Threshold Range: -9.9 to +9.9 volts in 0.1V increments.

**Threshold Setting:**

Threshold levels may be defined for pods 1, 2, and 3 on an individual basis and

one threshold may be defined for pods 4 and 5.

**Dynamic Range:**  $\pm$  10 volts about the threshold.

Minimum Input Overdrive: 250 mV or 30% of the input amplitude, whichever is greater.

Maximum Voltage: ±40 volts peak.

## **Measurement Configurations**

Analyzer Configurations: Analyzer 1 Analyzer 2

Timing Off

Off Timing

State Off

Off State

Timing State

State Timing

State State

Off Off

#### **Channel Assignment:**

Each group of 16 channels (a pod) can be assigned to Analyzer 1, Analyzer 2, or remain unassigned. The HP 16510B contains 5 pods.

### **State Analysis**

#### Memory

Data Acquisition: 1024 samples/channel.

#### **Trace Specification**

#### Clocks:

Five clocks are available and can be used by either one or two state analyzers at any time. Clock edges can be ORed together and operate in single phase, two phase demultiplexing, or two phase mixed mode. Clock edge is selectable as positive, negative, or both edges for each clock.

#### **Clock Qualifier:**

The high or low level of up to four clocks can be ANDed with the clock specification. Setup time: 20 ns; hold time: 5 ns.

#### Pattern Recognizers:

Each recognizer is the AND combination of bit (0, 1, or X) patterns in each label. Eight pattern recognizers are available when one state analyzer is on. Four are available to each analyzer when two state analyzers are on.

#### Range Recognizers:

Recognizes data which is numerically between or on two specified patterns (ANDed combination of 0s and/or 1s). One range term is available and is assigned to the first state analyzer turned on. The maximum size is 32 bits.

#### Qualifier:

A user-specified term that can be anystate, nostate, a single pattern recognizer, range recognizer, or logical combination of pattern and range recognizers.

#### **Sequence Levels:**

There are eight levels available to determine the sequence of events required for trigger. The trigger term can occur anywhere in the first seven sequence levels.

#### **Branching:**

Each sequence level has a branching qualifier. When satisfied, the analyzer will restart the sequence or branch to another sequence level.

#### **Occurrence Counter:**

Sequence qualifier may be specified to occur up to 65535 times before advancing to the next level.

#### Storage Qualification:

Each sequence level has a storage qualifier that specifies the states that are to be stored.

#### Enable/Disable:

Defines a window of post-trigger storage. States stored in this window can be qualified.

#### Prestore:

Stores two qualified states that precede states that are stored.

#### **Tagging**

#### **State Tagging:**

Counts the number of qualified states between each stored state.

Measurement can be shown relative to the previous state or relative to trigger. Maximum count is  $4.4 \times 10^{12}$ .

#### Time Tagging:

Measures the time between stored states, relative to either the previous state or the trigger. Maximum time between states is 48 hours.

With tagging on, the acquisition memory is halved; minimum time between states is 60 ns.

#### **Symbols**

#### **Pattern Symbols:**

User can define a mnemonic for the specific bit pattern of a label. When data display is SYMBOL, mnemonic is displayed where the bit pattern occurs. Bit pattern can include 0s, 1s, and don't cares.

#### Range Symbols:

User can define a mnemonic covering a range of values. Bit pattern for lower and upper limits must be defined as a pattern of 0s and 1s. When data display is SYMBOL, values within the specified range are displayed as mnemonic + offset from base of range.

Number of Pattern and Range Symbols: Combined total (both analyzer machines) of 200.

Symbols can be down-loaded over RS-232-C.

## **Timing Analysis**

## **Transitional Timing Mode**

Sample is stored in acquisition memory only when the data changes. A time tag stored with each sample allows reconstruction of waveform display. Time covered by a full memory acquisition varies with the number of pattern changes in the data.

Sample Period: 10 ns.

Maximum Time Covered By Data: 5000 seconds.

Minimum Time Covered by Data:  $10.24 \mu s$ .

#### **Glitch Capture Mode**

Data sample and glitch information stored every sample period.

Sample Period:

20 ns to 50 ms in a 1-2-5 sequence dependent on s/div and delay settings.

**Memory Depth:**

512 samples/channel.

Time Covered by Data: Sample period X 512.

#### **Waveform Display**

Sec/div:

10 ns to 100 s; 0.01% resolution.

Delay:

-2500 s to 2500 s; presence of data dependent on the number of transitions in data between trigger and trigger plus delay (transitional timing).

Accumulate:

Waveform display is not erased between successive acquisitions.

Overlay Mode:

$\label{eq:multiple} \text{Multiple channels can be displayed on one waveform display line. Primary use}$

is to view summary of bus activity.

Maximum Number Of Displayed Waveforms: 24

Table 1-2. HP 16510B Operating Characteristics (cont.)

#### **Time Interval Accuracy**

Channel to Channel Skew: 4 ns typical.

**Time Interval Accuracy:**

$\pm$  (sample period + channel-to-channel skew + 0.01% of time interval reading).

#### **Trigger Specification**

#### **Asynchronous Pattern:**

Trigger on an asynchronous pattern less than or greater than specified duration. Pattern is the logical AND of specified low, high, or don't care for each assigned channel. If pattern is valid but duration is invalid, there is a 20 ns reset time before looking for patterns again.

#### **Greater Than Duration:**

Minimum duration is 30 ns to 10 ms with 10 ns or 0.01% resolution, whichever is greater. Accuracy is +0 ns to -20 ns. Trigger occurs at pattern + duration.

#### **Less Than Duration:**

Maximum duration is 40 ns to 10 ms with 10 ns or 0.01% resolution, whichever is greater. Pattern must be valid for at least 20 ns. Accuracy is +20 ns to -0 ns. Trigger occurs at the end of the pattern.

#### Glitch/Edge Triggering:

Trigger on glitch or edge following valid duration of asynchronous pattern while the pattern is still present. Edge can be specified as rising, falling or either. Less than duration forces glitch and edge triggering off.

## **Measurement and Display Functions**

#### **Autoscale (Timing Analyzer Only)**

Autoscale searches for and displays channels with activity on the pods assigned to the timing analyzer.

#### **Acquisition Specifications**

#### Arming:

Each analyzer can be armed by the run key, the other analyzer, or the Intermodule Bus.

#### **Trace Mode:**

Single mode acquires data once per trace specification; repetitive mode repeats single mode acquisitions until stop is pressed or until time interval between two specified patterns is less than or greater than a specified value, or within or not within a specified range. There is only one trace mode when two analyzers are on.

#### Labels

Channels may be grouped together and given a six character name. Up to 20 labels in each analyzer may be assigned with up to 32 channels per label. Primary use is for naming groups of channels such as address, data, and control busses.

#### **Indicators**

#### **Activity Indicators:**

Provided in the Configuration, State Format, and Timing Format menus for identifying high, low, or changing states on the inputs.

#### Markers:

Two markers (X and 0) are shown as dashed lines on the display.

#### Trigger:

Displayed as a vertical dashed line in the timing waveform display and as line 0 in the state listing display.

#### **Marker Functions**

#### Time Interval:

The X and 0 markers measure the time interval between one point on a timing waveform and trigger, two points on the same timing waveform, two points on different waveforms, or two states (time tagging on).

#### **Delta States (State Analyzer Only):**

The X and 0 markers measure the number of tagged states between one state and trigger, or between two states.

#### Patterns:

The X and 0 markers can be used to locate the nth occurrence of a specified pattern before or after trigger, or after the beginning of data. The 0 marker can also find the nth occurrence of a pattern before or after the X marker.

#### Statistics:

X to 0 marker statistics are calculated for repetitive acquisitions. Patterns must be specified for both markers and statistics are kept only when both patterns can be found in an acquisition. Statistics are minimum X to 0 time, maximum X to 0 time, average X to 0 time, and ratio of valid runs to total runs.

#### **Run/Stop Functions**

Run:

Starts acquisition of data in specified trace mode.

Stop:

In single trace mode or the first run of a repetitive acquisition, STOP halts acquisition and displays the current acquisition data. For subsequent runs in repetitive mode, STOP halts acquisition of data and does not change current display.

#### Data Display/Entry

#### **Display Modes:**

State listing; timing waveforms; interleaved, time-correlated listing of two state analyzers (time tagging on); time-correlated state listing and timing waveform display (state listing in upper half, timing waveform in lower half, and time tagging on).

**Timing Waveform:** Pattern readout of timing waveforms at X or 0 marker.

Bases: Binary, Octal, Decimal, Hexadecimal, ASCII (display only), and User-defined symbols.

## **Auxiliary Power**

**Power Through Cables:**

2/3 amp @ 5V maximum per cable.

**Current Draw Per Card:**

2 amp @ 5V maximum per HP 16510B

## **Operating Environment**

Temperature:

Instrument, 0  $^{\circ}$  to 55  $^{\circ}$  C (+32  $^{\circ}$  to 131  $^{\circ}$  F). Probe lead sets and cables,

0  $^{\circ}$  to 65  $^{\circ}$  C (+32  $^{\circ}$  to 149  $^{\circ}$  F).

**Humidity:**

Instrument, up to 95% relative humidity at +40  $^{\circ}$  C (+122  $^{\circ}$  F).

Altitude:

To 4600 m (15,000 ft).

Vibration:

Operation: Random vibration 5-500 Hz, 10 minutes per axis, ~0.3 g (rms).

Non-operating: Random vibration 5-500 Hz, 10 minutes per axis,  $\sim$  2.41 g (rms); and swept sine resonant search, 5-500 Hz, 0.75 g (0-peak), 5 minute

resonant dwell @ 4 resonances per axis.

Table 1-3. Recommended Test Equipment

| Instrument                                                  | Critical Specification                            | Recommended<br>Model | Use* |

|-------------------------------------------------------------|---------------------------------------------------|----------------------|------|

| DMM                                                         | 3 1/2 DIGIT RESOLUTION                            | HP 3478A             | А    |

| PULSE<br>GENERATOR                                          | 5 ns PULSE WIDTH, 20 ns PERIOD<br>1.3 ns RISETIME | HP 8161A/020         | Р    |

| OSCILLOSCOPE                                                | DUAL CHANNEL, 300 MHz BANDWIDTH                   | HP 54201A            | Р    |

| POWER SUPPLY                                                | + 10.2 V TO - 10.2 V OUTPUT; CURRENT 0-0.4 AMP    | HP 6216B             | Р    |

| 50 OHM<br>FEEDTHRU                                          | QTY. 2                                            | HP 10100C            | Р    |

| BNC TEE                                                     | 1 MALE, 2 FEMALE QTY 2                            | HP 1250-0781         | Р    |

| BNC Cable                                                   | (M-M) 48 INCH QTY 4                               | HP 10503A            | Р    |

| EXTENDER<br>BOARD                                           | NO SUBSTITUTE                                     | HP 16500-69004       | A    |

| TEST<br>CONNECTOR                                           | BNC (F) PANEL MOUNT                               | HP 1250-1032         | Р    |

|                                                             |                                                   |                      |      |

| * A = Adjustments P = Performance Tests T = Troubleshooting |                                                   |                      |      |

## **TABLE OF CONTENTS**

#### Installation

| 2-1.  | Introduction             | 2-1 |

|-------|--------------------------|-----|

| 2-2.  | Initial Inspection       | 2-1 |

| 2-3.  | Preparation For Use      | 2-1 |

| 2-4.  | Power Requirements       | 2-1 |

| 2-5.  | Safety Requirements      | 2-1 |

| 2-6.  | Probe Cable Installation | 2-1 |

| 2-7.  | Module Installation      | 2-1 |

| 2-8.  | Operating Environment    | 2-4 |

| 2-9.  | Storage                  | 2-4 |

| 2-10. | Packaging                | 2-4 |

|       | Tagging For Service      |     |

# SECTION II Installation

#### 2-1. Introduction

This section explains, how to initially inspect the HP 16510B State/Timing Module, how to prepare it for use, storage and shipment. Also included are procedures for module installation.

#### 2-2. Initial Inspection

Inspect the shipping container for damage. If the shipping container or cushioning material is damaged, it should be kept until the contents of the shipment have been checked for completeness and the module has been checked mechanically and electrically. The contents of the shipment should be as listed in the "Accessories Supplied" paragraph located in Section 1.

Procedures for checking electrical performance are in Section 3. If the contents of the container are incomplete, there is mechanical damage or defect, or the instrument does not pass the performance tests, notify the nearest Hewlett-Packard office.

If the shipping container is damaged, or the cushioning material shows signs of stress, notify the carrier as well as the Hewlett-Packard office. Keep the shipping material so the carrier can inspection it. The Hewlett-Packard office will arrange for repair or replacement at Hewlett-Packard's option without waiting for claim settlement.

#### 2-3. Preparation for Use

WARNING

Read the Safety Considerations in the front of this manual and in Section I before installing or operating this module.

#### 2-4. Power Requirements

All power supplies required for operating the HP 16510B State/Timing Module are supplied to the module through the backplane connector.

#### 2-5. Safety Requirements

Specific warnings, cautions, and instructions are placed wherever applicable throughout the manual. These must be observed during all phases of operation, service, and repair of the module. Failure to comply with them violates safety standards of design, manufacture, and intended use of this module. Hewlett-Packard assumes no liability for the failure of the customer to comply with these safety requirements.

#### 2-6. Probe Cable Installation

The HP 16510B State/Timing Module comes with probe cables installed by the factory. If a cable is to be switched or replaced, refer to "Probe Cable Replacement" in Section 6 of this manual.

#### 2-7. Module Installation

CAUTION

Do not install, remove or replace the module in the instrument unless the instrument power is turned off.

The HP 16510B State/Timing Module will take up one slot in the card cage. For every additional HP 16510B State/Timing Module you install, you will need an additional slot. They may be installed in any slot and in any order. The installation procedure for the module is continued, step-by-step, on the next page.

## **Module Installation (cont.)**

## CAUTION

The effects of ELECTROSTATIC DISCHARGE can damage electronic components. Use grounded wriststraps and mats when you are performing any kind of service to this module.

#### **Installation Considerations**

- The HP 16510B State/Timing Module(s) can be installed in any available card slot and in any order.

- Cards or filler panels below the empty slots intended for module installation do not have to be removed.

- The probe cables do not have to be removed to install the module.

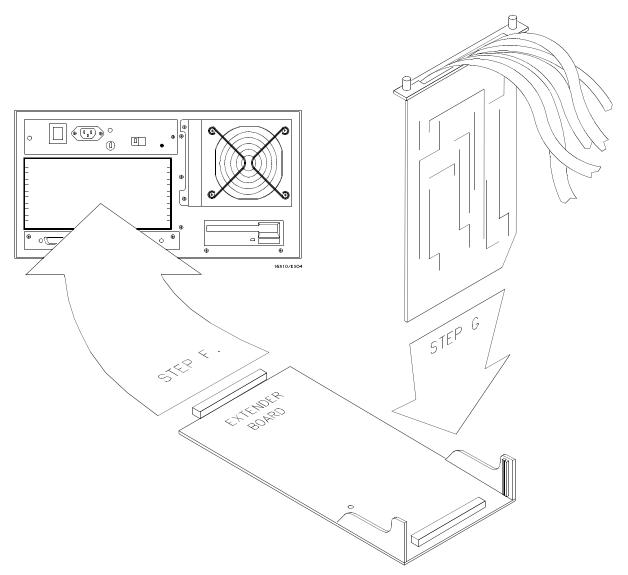

#### **Procedure**

- a. Turn instrument power switch off, unplug power cord and disconnect any input connections.

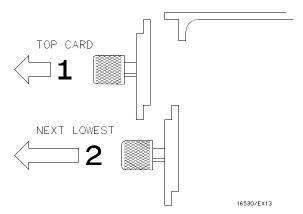

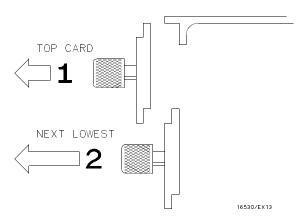

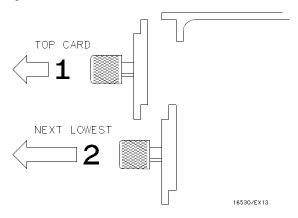

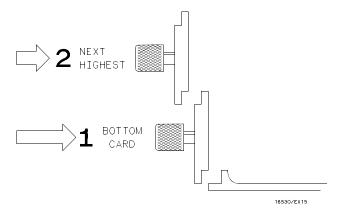

- b. Starting **from the top**, loosen thumb screws on filler panel(s) and card(s).

- c. Starting from the top, begin pulling card(s) and filler panel(s) out half way. See figure 2-1.

Figure 2-1. Endplate Overlap

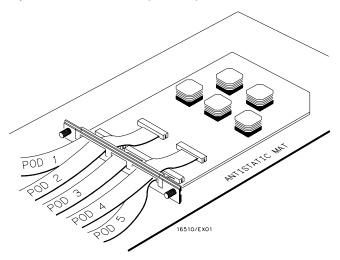

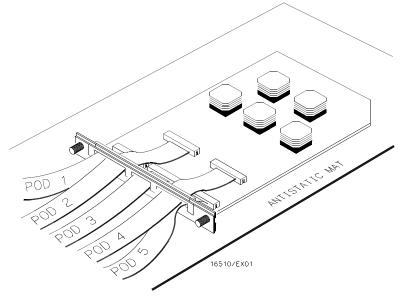

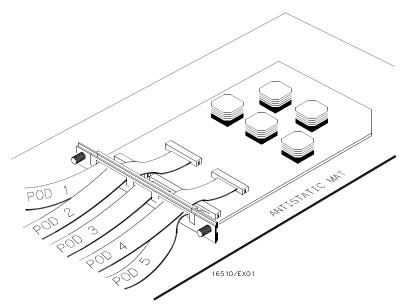

- d. Lay the cable(s) flat and pointing out to the rear of the card. See figure 2-2.

- e. Slide the analyzer card approximately half way into the card cage.

- f. If you have more analyzer cards to install repeat step d and e.

Figure 2-2. Cable Position

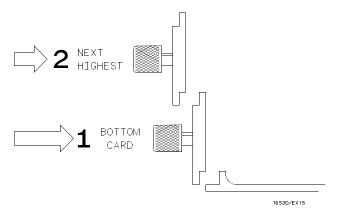

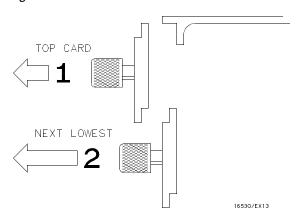

- g. Firmly seat bottom card into backplane connector. Keep applying pressure to the center of card endplate while tightening thumb screws finger tight.

- h. Repeat for all cards and filler panels in a bottom to top order. See figure 2-3.

Figure 2-3. Endplate Overlap

i. Any filler panels that are not used should be kept for future use. Filler panels **must** be installed in all unused card slots for correct air circulation.

2-3

#### 2-8. Operating Environment

The operating environment is listed in table 1-2 of Section 1 of this manual. Note should be made of the non-condensing humidity limitation. Condensation within the instrument can cause poor operation or malfunction. Protection should be provided against internal condensation.

The HP 16510B State/Timing Card will operate at all specifications within the temperature and humidity range given in table 1-2. However, reliability is enhanced when operating the module within the following ranges.

• **Temperature**: +20°C to +35°C (+68°F to +95°F)

• Humidity: 20% to 80% non-condensing

#### 2-9. Storage

The module may be stored or shipped in environments within the following limits:

• Temperature: -40°C to +75°C

• Humidity: Up to 90% at 65°C

Altitude: Up to 15,300 meters (50,000 feet)

The module should also be protected from temperature extremes which cause condensation on the module.

#### 2-10. Packaging

The following general instructions should be used for repacking the module with commercially available materials.

- Wrap module in anti-static plastic.

- Use a strong shipping container. A doublewall carton made of 350 lb. test material is adequate.

- Use a layer of shock-absorbing material 70 to 100 mm (3 to 4 inch) thick around all sides of the module to provide firm cushioning and prevent movement inside the container.

- Seal shipping container securely.

- Mark shipping container FRAGILE to ensure careful handling.

- In any correspondence, refer to module by model number and board number.

#### 2-11. Tagging for Service

If the module is to be shipped to a Hewlett-Packard office for service or repair, attach a tag showing owner (with address), complete board number, and a description of the service required.

## **TABLE OF CONTENTS**

## SECTION III Performance Tests

| 3-1.  | Introduction                             | 3-1  |

|-------|------------------------------------------|------|

| 3-2.  | Recommended Test Equipment               | 3-1  |

| 3-3.  | Test Record                              | 3-1  |

| 3-4.  | Performance Test Interval                | 3-1  |

| 3-5.  | Performance Test Procedures              | 3-1  |

| 3-6.  | Test Connector                           | 3-1  |

| 3-7.  | Clock, Qualifier, and Data Input Tests 1 | 3-2  |

| 3-8.  | Clock, Qualifier, and Data Input Tests 2 | 3-7  |

|       | Clock, Qualifier, and Data Input Tests 3 |      |

| 3-10. | Clock, Qualifier, and Data Input Tests 4 | 3-13 |

| 3-11. | Clock, Qualifier, and Data Input Tests 5 | 3-16 |

| 3-12. | Clock, Qualifier, and Data Input Tests 6 | 3-19 |

| 3-13. | Clock, Qualifier, and Data Input Tests 7 | 3-22 |

| 3-14. | Glitch Test                              | 3-25 |

| 3-15. | Threshold Accuracy Test                  | 3-29 |

# SECTION III Performance Tests

#### 3-1. Introduction

The procedures in this section test the HP 16510B State/Timing Analyser's electrical performance using the specifications listed in Section I as the performance standards. All tests can be performed without access to the interior of the instrument. At the end of this section is a form that can be used as a record of performance test results.

#### 3-2. Recommended Test Equipment

Equipment recommended for performance tests is listed in table 1-3. Any equipment that satisfies the critical specifications given in the table may be substituted for the recommended models.

#### 3-3. Test Record

Results of performance tests may be tabulated on the Performance Test Record (table 3-1) at the end of the procedures. The test record lists all of the tested specifications and their acceptable limits. The results recorded on the test record may be used for comparison in periodic maintenance and troubleshooting or after repairs and adjustments have been made.

#### 3-4. Performance Test Interval

Periodic performance verification of the HP 16510B State/Timing Module is required at two year intervals. The instrument's performance should be verified after it has been serviced, or if improper operation is suspected. Further checks requiring access to the interior of the instrument are included in the adjustment section, but are not required for the performance verification.

#### 3-5. Performance Test Procedures

All performance tests should be performed at the instruments environmental operating temperature and after a 15-minute warm up period.

#### 3-6. Test Connector

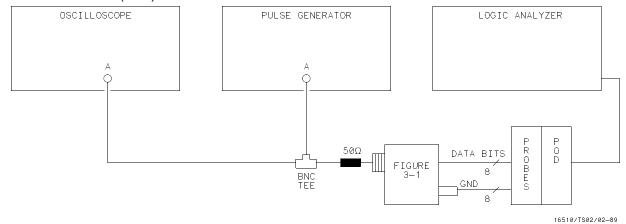

The performance tests and adjustments require connecting pulse generator outputs to probe pod inputs. Figure 3-1 is a test connector that may be built to allow testing of multiple channels (up to eight at one time). The test connector consists of a BNC connector and a length of wire. Connecting more than eight channels to the test connector at a time will induce loading of the circuit and true signal representation will degrade. Test results may not be accurate if more than eight channels are connected to the test connector.

The Hewlett-Packard part number for the BNC connector in figure 3-1 is 1250-1032. An equivalent part may be used in place of the Hewlett-Packard part.

Figure 3-1. Test Connector

#### 3-7. Clock, Qualifier, and Data Inputs Test 1

#### **Description:**

This performance test verifies maximum clock rate with counting mode and the setup and hold times for the falling edge of all clocks to pods 1, 3, and 5.

#### Specification:

Clock repetition rate: With time or state counting mode on, minimum time between states is 60 ns.

Hold time: Data must be present after falling edge of all clocks; 0 ns.

Setup time: Data must be present prior to clock transition;≥ 10ns.

#### **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        |              |

| BNC Cable (4)                      |              |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

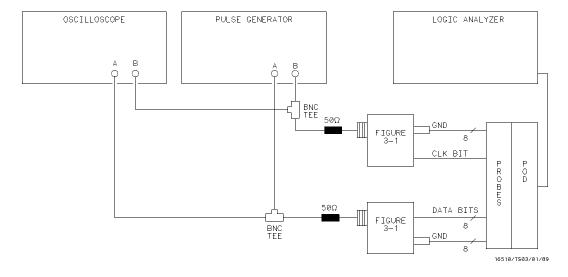

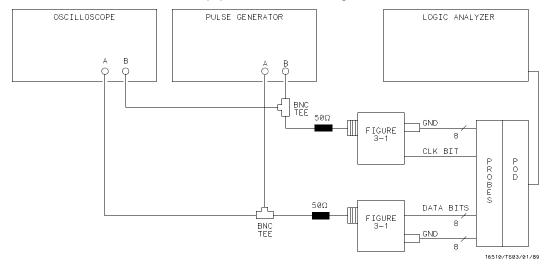

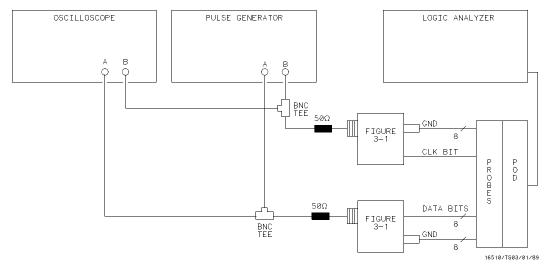

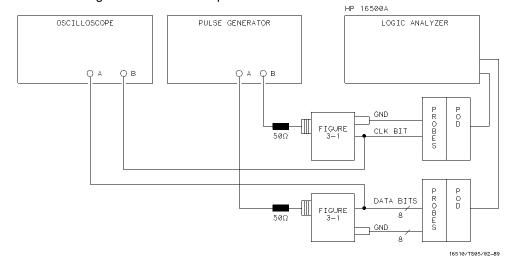

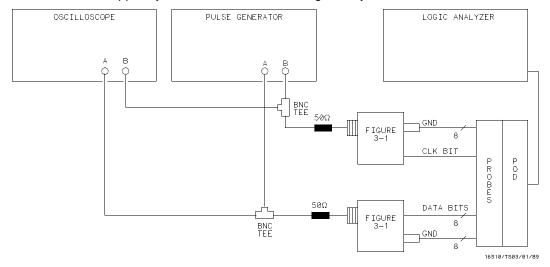

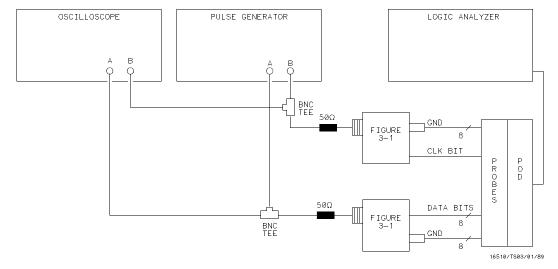

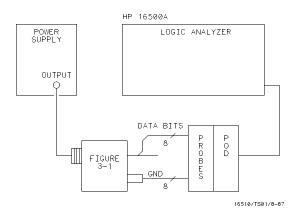

1. Connect the HP 16510B and test equipment as shown in figure 3-2.

Figure 3-2. Equipment Setup For Test 1

#### **Note**

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

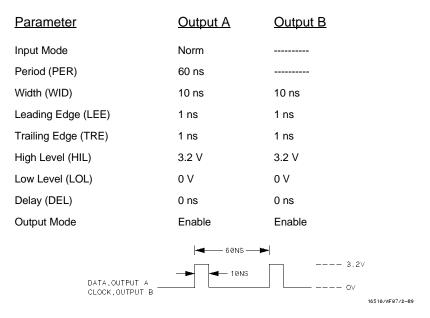

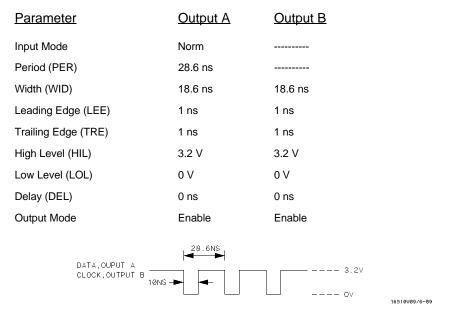

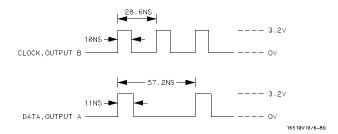

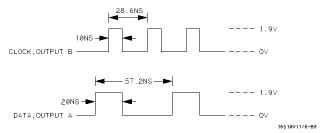

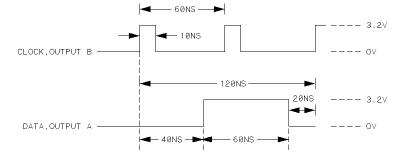

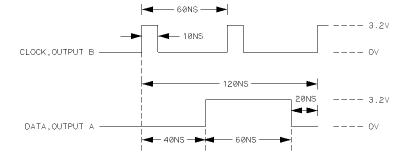

2. Set the pulse generator as follows for the output shown in figure 3-3.

#### Setting for the HP 8161A:

Figure 3-3. Pulse Generator Waveform For Test 1

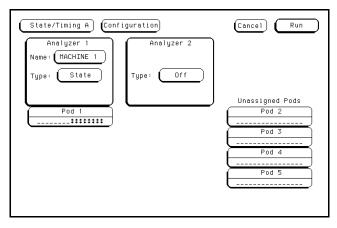

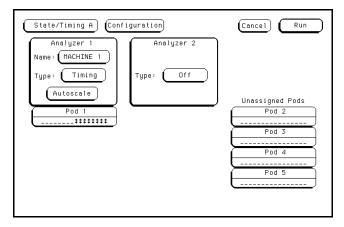

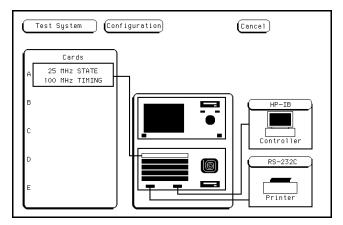

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as shown in figure 3-4. Refer to steps *a* and *b* if unfamiliar with menus.

- a. Touch Type field of Analyzer 1, then touch State.

- b. Touch the Pod field of pod to be tested, then touch Analyzer 1.

Figure 3-4. Configuration Screen

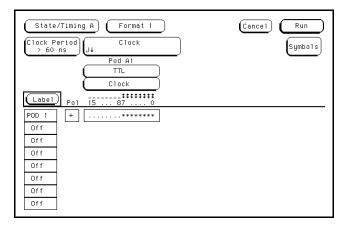

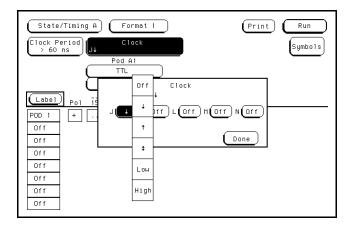

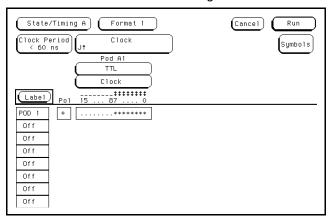

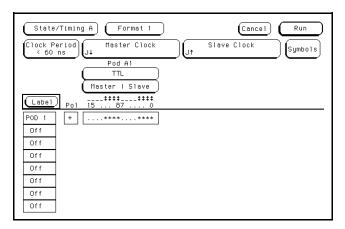

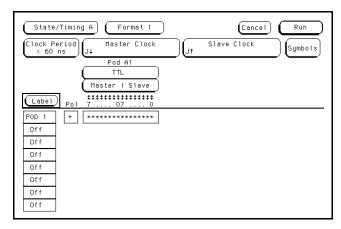

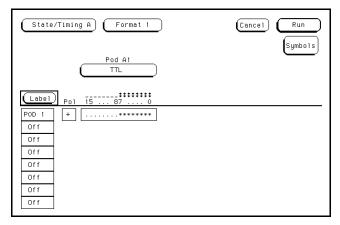

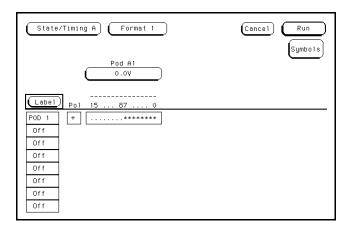

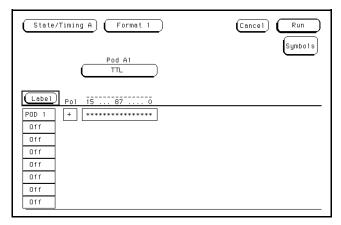

4. Assign appropriate clock, a falling edge, a clock period > 60 ns, and bits 0 through 7 of the pod under test to a label in the Format screen as shown in figure 3-5. Refer to steps *a* and *b* if unfamiliar with the menus.

Figure 3-5. Format Screen for Pod 1 and J Clock Test

a. Touch top most Clock field and set appropriate clock for a falling edge. See figure 3-6. Each pod contains one clock line. The clock line on pod 1 is the J clock; the clock line on pod 2 is the K clock; etc.

Figure 3-6. Format Screen/Clock Assignment

b. Touch the Bit Assignment field and turn on bits 0 through 7 (asterisk (\*) = on; dot (.) = off). See figure 3-7.

Figure 3-7. Format Screen/Bit Assignment

- 5. Configure the Trace screen without sequencing levels and set Count to States as shown in figure 3-8. Refer to steps *a* and *b* if unfamiliar with the menus.

- a. Touch Count, then States, then touch Anystate.

- b. Touch **Prestore**, then touch **Off**.

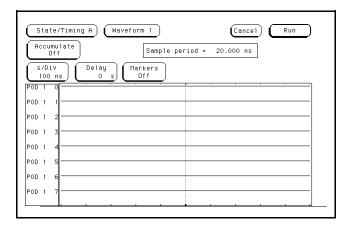

Figure 3-8. Trace Screen

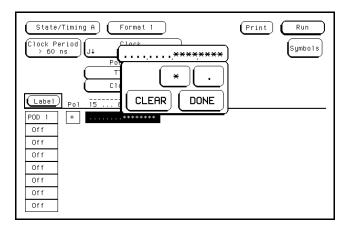

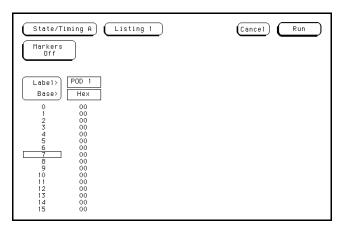

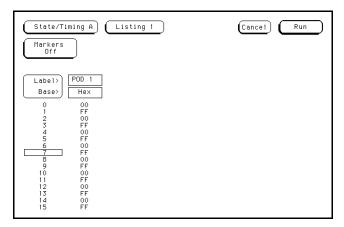

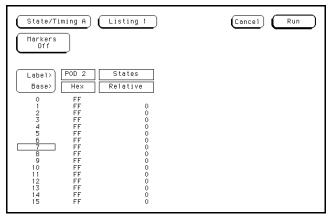

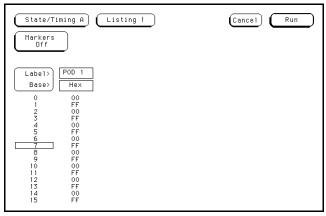

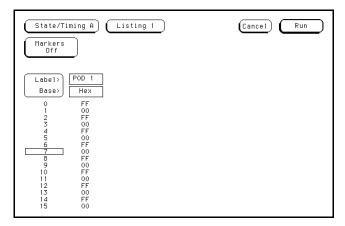

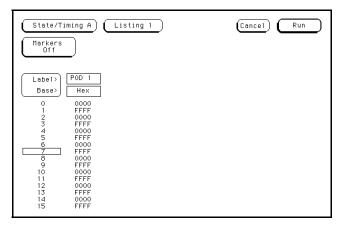

6. Touch **Run**. The State Listing screen will be displayed and should show all F's for the channels under test. See figure 3-9.

Figure 3-9. Listing Screen

#### **Note**

To ensure a consistent pattern of F's in listing, use Roll field and knob to scroll through State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clock lines J, K, L, M and N).

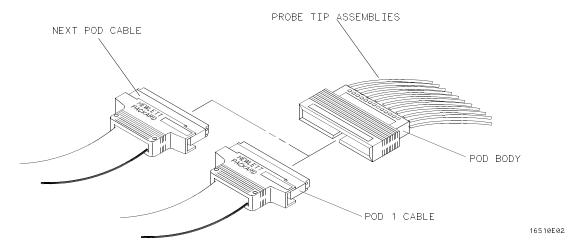

- 8. Remove the pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1, 3 and 5). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect lower eight bits from test connector. Attach bits 8 through 15 to test connector and repeat steps 3, 4, 6, 7 and 8 until upper eight bits of all pods have been tested (pods 1, 3 and 5).

Figure 3-10. Switching To Next Probe Cable

## 3-8. Clock, Qualifier, and Data Inputs Test 2

#### **Description:**

This performance test verifies the setup and hold time specification for the rising edge transition of all clocks.

#### Specification:

Setup Time: Data must be present prior to clock transition; ≥10 ns.

Hold Time: Data must be present after rising clock transition; 0 ns.

#### **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        | HP 1250-0781 |

| BNC Cable (4)                      |              |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

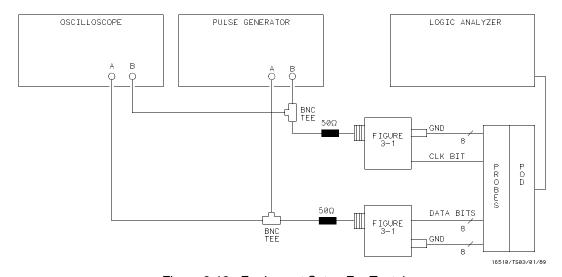

1. Connect the HP 16510B and test equipment as shown in figure 3-11.

Figure 3-11. Equipment Setup For Test 2

#### **Note**

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-12.

#### Setting for the HP 8161A:

Figure 3-12. Pulse Generator Waveform For Test 2

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as shown in figure 3-4.

- 4. Assign appropriate clock, a rising edge, a clock period < 60 ns, and bits 0 through 7 of the pod under test to a label in the Format screen as shown in figure 3-13.

Figure 3-13. Format Screen

(Cancel) State/Timing A Run Trace 1 Branches Off Store "anystate" Count Off Prestore Off POD 1 Label: Base> Hex VV XX b XX

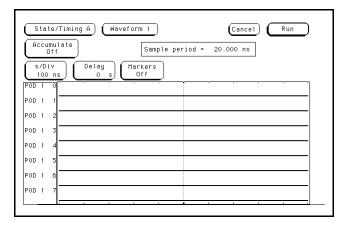

5. Configure the Trace screen without sequencing levels and set Count to Off as shown in figure 3-14.

Figure 3-14. Trace Screen

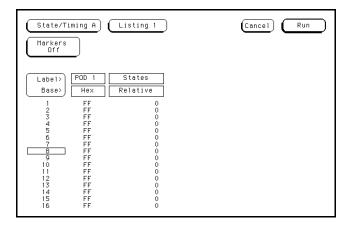

6. Touch **Run**. The State Listing screen will be displayed and should show all 0's for the channels under test. See figure 3-15.

Figure 3-15. Listing Screen

#### Note

To ensure a consistent pattern of 0's in listing, use Roll field and knob to scroll through State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clock lines J, K, L, M and N).

- 8. Remove the pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1 through 5). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect lower eight bits from test connector. Attach bits 8 through 15 to test connector and repeat steps 3, 4, 6, 7 and 8 until upper eight bits of all pods have been tested (pods 1 through 5).

## 3-9. Clock, Qualifier, and Data Inputs Test 3

#### **Description:**

This performance test verifies the hold time specifications for the falling clock transitions of all clocks to pods 2 and 4.

#### Specification:

Hold Time: Data must be present after falling clock transitions; 1 ns.

#### **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        |              |

| BNC Cable (4)                      | HP 10503A    |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

1. Connect the HP 16510B and test equipment as in figure 3-16.

Figure 3-16. Equipment Setup For Test 3

#### **Note**

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-17.

#### Setting for the HP 8161A:

| <u>Parameter</u>    | Output A | Output B |

|---------------------|----------|----------|

| Input Mode          | Norm     |          |

| Period (PER)        | 57.2 ns  |          |

| Width (WID)         | 11 ns    | 10 ns    |

| Leading Edge (LEE)  | 1 ns     | 1 ns     |

| Trailing Edge (TRE) | 1 ns     | 1 ns     |

| High Level (HIL)    | 3.2 V    | 3.2 V    |

| Low Level (LOL)     | 0 V      | 0 V      |

| Delay (DEL)         | 0 ns     | 0 ns     |

| Double Pulse        |          | 28.6 ns  |

| Output Mode         | Enable   | Enable   |

Figure 3-17. Pulse Generator Waveform For Test 3

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as in previous test figure 3-4.

- 4. Assign appropriate clock, a falling edge, clock period < 60 ns, and bits 0 through 7 of the pod under test to a label in the Format screen. See figure 3-13.

- 5. Configure the Trace screen without sequencing levels and set Count to Off as shown in figure 3-14.

6. Touch **Run**. The State Listing screen will be displayed and should list alternate F's and 0's as shown in figure 3-18.

Figure 3-18. Listing Screen

#### **Note**

To ensure a consistent pattern of alternating F's and 0's, use the Roll field and knob to scroll through the State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clocks lines J, K, L, M and N).

- 8. Remove the pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 2 and 4). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect lower eight bits from test connector. Attach bits 8 through 15 to test connector and repeat steps 3, 4, 6, 7 and 8 until upper eight bits of all pods have been tested (pods 2 and 4).

## 3-10. Clock, Qualifier, and Data Inputs Test 4

## **Description:**

This performance test verifies maximum clock rate with counting mode and the setup times for the falling edge of all clocks to pods 2 and 4.

## Specification:

Clock repetition rate: With time or state counting mode on, minimum time between states is 60 ns.

Setup time: Data must be present prior to clock transition, ≥ 10ns.

## **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        | HP 1250-0781 |

| BNC Cable (4)                      |              |

| Test Connectors (2) see figure 3-1 |              |

## Procedure:

1. Connect the HP 16510B and test equipment as in figure 3-19.

Figure 3-19. Equipment Setup For Test 4

### Note

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-20.

## Setting for the HP 8161A:

| <u>Parameter</u>    | Output A     | Output B           |

|---------------------|--------------|--------------------|

| Input Mode          | Norm         |                    |

| Period (PER)        | 60 ns        |                    |

| Width (WID)         | 11 ns        | 10 ns              |

| Leading Edge (LEE)  | 1 ns         | 1 ns               |

| Trailing Edge (TRE) | 1 ns         | 1 ns               |

| High Level (HIL)    | 3.2 V        | 3.2 V              |

| Low Level (LOL)     | 0 V          | 0 V                |

| Delay (DEL)         | 0 ns         | 0 ns               |

| Output Mode         | Enable       | Enable             |

|                     | 60NS         | ¬ 3.2V             |

| CLOCK,OUTPUT B      | <b></b> 10NS | ov                 |

| •                   | 60NS         | 3.2V               |

| DATA,OUPUT A        | 1            | OV 1651@/WF@8/7-87 |

Figure 3-20. Pulse Generator Waveform For Test 4

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as in previous test figure 3-4.

- 4. Assign appropriate clock, a falling edge, clock period > 60 ns, and bits 0 through 7 of the pod under test to a label in the Format screen. See figure 3-5.

- 5. Configure the Trace screen without sequencing levels and set Count to States. See figure 3-8.

6. Touch **Run**. The State Listing screen will be displayed and should list all F's as shown in figure 3-21.

Figure 3-21. Listing Screen

## **Note**

To ensure a consistent pattern of F's in the listing, use the Roll field and knob to scroll through the State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clocks lines J, K, L, M and N).

- 8. Remove the pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 2 and 4). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect lower eight bits from test connector. Attach bits 8 through 15 to test connector and repeat steps 3, 4, 6, 7 and 8 until upper eight bits of all pods have been tested (pods 2 and 4).

## 3-11. Clock, Qualifier, and Data Inputs Test 5

## **Description:**

This performance test verifies the minimum swing voltages of the input probes and the maximum clock rate of the HP 16510B when it is in single phase mode.

## Specification:

Minimum swing: 600 mV peak-to-peak.

Clock repetition rate: Single phase is 35 MHz maximum.

Clock pulse width: ≥ 10 ns at threshold.

## **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                | HP 10100C    |

| BNC Cable (2)                      | HP 10503A    |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

1. Connect the HP 16510B and test equipment as in figure 3-22. In order to most accurately measure the amplitude of the test signals from the pulse generator, high impedance scope probes should be used to look at the signal levels at the output of the BNC test connector.

Figure 3-22. Equipment Setup For Test 5

#### Note

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-23.

## Setting for the HP 8161A:

| <u>Parameter</u>    | Output A | <u>Output</u> | <u>B</u>         |

|---------------------|----------|---------------|------------------|

| Input Mode          | Norm     |               |                  |

| Period (PER)        | 57.2 ns  |               |                  |

| Width (WID)         | 20 ns    | 10 ns         |                  |

| Leading Edge (LEE)  | 1 ns     | 1 ns          |                  |

| Trailing Edge (TRE) | 1 ns     | 1 ns          |                  |

| High Level (HIL)    | 1.9 V    | 1.9 V         | (see Note below) |

| Low Level (LOL)     | 1.3 V    | 1.3 V         | (see Note below) |

| Delay (DEL)         | 18.6 ns  | 0 ns          |                  |

| Double Pulse        |          | 28.6 ns       |                  |

| Output Mode         | Enable   | Enable        |                  |

|                     |          |               |                  |

Figure 3-23. Pulse Generator Waveform For Test 5

### **Note**

The voltage levels of the waveforms must have the correct amplitude at the logic analyzer probe tips. The pulse generator output may have to be increased slightly to compensate for the loading by the logic analyzer.

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as shown in figure 3-4.

- 4. Assign appropriate clock, a rising edge, clock period < 60 ns, and bits 0 through 7 of the pod under test to a label in the Format screen. See figure 3-13.

- 5. Configure the Trace screen without sequencing levels and set Count to Off. See figure 3-14.

6. Touch **Run**. The State Listing screen will be displayed and should list alternating F's and 0's as shown in figure 3-24.

Figure 3-24. Listing Screen

#### **Note**

To ensure a consistent pattern of alternating F's and 0's, use the Roll field and knob to scroll through the State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clocks lines J, K, L, M and N).

- 8. Remove pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1 through 5). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect lower eight bits from test connector. Attach bits 8 through 15 to test connector and repeat steps 3, 4, 6, 7 and 8 until upper eight bits of all pods have been tested (pods 1 through 5).

## 3-12. Clock, Qualifier, and Data Inputs Test 6

#### **Description:**

This performance test verifies the maximum clock rate for mixed mode clocking during state operation.

#### Specification:

Clock repetition rate: Single phase is 35 MHz maximum. With time or state counting, minimum time between states is 60 ns. Both mixed and demultiplexed clocking use master-slave clock timing; master clock must follow slave clock by at least 10 ns and precede the next slave clock by > 50 ns.

## **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        |              |

| BNC Cable (4)                      |              |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

1. Connect the HP 16510B and test equipment as shown in figure 3-25. Connect channels 0 through 3 and 8 through 11 of the pod under test to the test connector. On the slave clock transition, the four bits of the lower byte are transferred to the logic analyzer, and on the master clock transition, the four bits of the upper byte are transferred to the logic analyzer.

Figure 3-25. Equipment Setup For Test 6

#### Note

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-26.

## Setting for the HP 8161A:

| <u>Parameter</u>    | Output A | Output B |

|---------------------|----------|----------|

| Input Mode          | Norm     |          |

| Period (PER)        | 120 ns   |          |

| Width (WID)         | 60 ns    | 10 ns    |

| Leading Edge (LEE)  | 1 ns     | 1 ns     |

| Trailing Edge (TRE) | 1 ns     | 1 ns     |

| High Level (HIL)    | 3.2 V    | 3.2 V    |

| Low Level (LOL)     | 0 V      | 0 V      |

| Delay (DEL)         | 40 ns    | 0 ns     |

| Double Pulse        |          | 60 ns    |

| Output Mode         | Enable   | Enable   |

|                     |          |          |

Figure 3-26. Pulse Generator Waveform For Test 6

16510/WF02/2-89

- 3. Assign the pod under test to Analyzer 1 in the Configuration screen as shown in figure 3-4.

- 4. Set up Format screen as in figure 3-27, assigning a falling clock edge as master clock and rising edge of same clock as slave clock. Refer to steps *a* through *c* if unfamiliar with the menus.

- a. Touch lower Clock field, then touch Mixed Clocks.

- b. Assign falling edge of the appropriate clock as master clock and rising edge of the same clock as slave clock.

- c. Assign the appropriate eight bits of pod under test (channels 0-3 and 8-11, or 4-7 and 12-15). The clock period should be set to < 60 ns.

Figure 3-27. Format Screen

- 5. Configure Trace screen without sequencing levels and set Count to Off. See figure 3-14.

- 6. Touch **Run**. The State Listing screen will be displayed and should list alternating F's and 0's as shown in figure 3-28.

Figure 3-28. Listing Screen

### **Note**

To ensure a consistent pattern of alternating F's and 0's, use the Roll field and knob to scroll through the State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clocks lines J, K, L, M and N).

- 8. Remove pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1 through 5). Make sure the appropriate pod and clock are assigned and all probe assemblies are still connected to the test connector.

- 9. Disconnect bits 0-3 and 8-11 from test connector. Attach bits 4-7 and bits 12-15 to test connector and repeat steps 3, 4, 6, 7 and 8 until all pods have been tested (pods 1 through 5).

## 3-13. Clock, Qualifier, and Data Inputs Test 7

#### **Description:**

This performance test verifies the maximum clock rate for demultiplexed clocking during state operation.

#### Specification:

Clock repetition rate: Single phase is 35 MHz maximum. With time or state counting, minimum time between states is 60 ns. Both mixed and demultiplexed clocking use master-slave clock timing; master clock must follow slave clock by at least 10 ns and precede the next slave clock by > 50 ns.

## **Equipment:**

| Pulse Generator                    | HP 8161A/020 |

|------------------------------------|--------------|

| Oscilloscope                       | HP 54201A    |

| 50 Ohm Feedthru (2)                |              |

| BNC Tee (2)                        |              |

| BNC Cable (4)                      |              |

| Test Connectors (2) see figure 3-1 |              |

#### Procedure:

Connect the HP 16510B and test equipment as shown in figure 3-29 by connecting channels 0 - 7

of the pod under test to test connector. During demultiplexed clocking only the lower eight bits of

each pod are used.

Figure 3-29. Equipment Setup For Test 7

#### Note

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

16510/WF02/2-89

2. Set the pulse generator as follows for the output shown in figure 3-30.

## Setting for the HP 8161A:

| <u>Parameter</u>    | Output A | Output B |

|---------------------|----------|----------|

| Input Mode          | Norm     |          |

| Period (PER)        | 120 ns   |          |

| Width (WID)         | 60 ns    | 10 ns    |

| Leading Edge (LEE)  | 1 ns     | 1 ns     |

| Trailing Edge (TRE) | 1 ns     | 1 ns     |

| High Level (HIL)    | 3.2 V    | 3.2 V    |

| Low Level (LOL)     | 0 V      | 0 V      |

| Delay (DEL)         | 40 ns    | 0 ns     |

| Double Pulse        |          | 60 ns    |

| Output Mode         | Enable   | Enable   |

|                     |          |          |

Figure 3-30. Pulse Generator Waveform For Test 7

- 3. Assign the pod under test to Analyzer 1 in Configuration screen as shown in figure 3-4.

- 4. Set up Format screen as in figure 3-31, assigning a falling clock edge as master clock and rising edge of same clock as slave clock. Refer to steps *a* through *c* if unfamiliar with the menus.

- a. Touch Master | Slave, then touch Demultiplex.

- b. Assign a falling edge of appropriate as master clock and a rising clock edge of same clock as slave clock.

- c. Assign all channels to pod under test (only bits 0 through 7 will be available for assignment). The Clock Period should be set to < 60 ns.

Figure 3-31. Format Screen

- 5. Configure Trace screen without sequencing levels and set Count to Off as shown in figure 3-14.

- 6. Touch **Run**. The State Listing screen will be displayed and should list alternating F's and 0's as shown in figure 3-32.

Figure 3-32. Listing Screen

### Note

To ensure a consistent pattern of alternating F's and 0's, use the Roll field and knob to scroll through the State Listing.

- 7. Connect the next clock line to the test connector and repeat steps 4 and 6. Repeat until all clocks have been tested (clocks lines J, K, L, M and N).

- 8. Remove pod body (with probe tip assemblies still connected to the test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4, 6 and 7 until all pods have been tested (pods 1 through 5). Make sure the appropriate pod and clock are assigned.

## 3-14. Glitch Test

## **Description:**

This performance test verifies the glitch detection specification.

## Specification:

Minimum detectable glitch: 5 ns wide at the threshold.

## **Equipment:**

| Pulse Generator                   | HP 8161A/020 |

|-----------------------------------|--------------|

| Oscilloscope                      | HP 54201A    |

| 50 Ohm Feedthru                   |              |

| BNC Tee                           | HP 1250-0781 |

| BNC Cable (2)                     | HP 10503A    |

| Test Connector (1) see figure 3-1 |              |

#### Procedure:

1. Connect the HP 16510B and test equipment as shown in figure 3-33. The clock inputs are not used for the glitch performance test. Using the oscilloscope, make sure the pulses are 5 ns wide at the threshold (1.6V).

Figure 3-33. Equipment Setup For Glitch Test

### **Note**

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results. Also, the oscilloscope must be high impedence.

2. Set the pulse generator as follows for the output shown in figure 3-34.

## Setting for the HP 8161A:

| <u>Parameter</u>    | Output A     | Output B   |                |

|---------------------|--------------|------------|----------------|

| Input Mode          | Norm         |            |                |

| Period (PER)        | 20 ns        |            |                |

| Width (WID)         | 5 ns         |            |                |

| Leading Edge (LEE)  | 1 ns         |            |                |

| Trailing Edge (TRE) | 1 ns         |            |                |

| High Level (HIL)    | 3.2 V        |            |                |

| Low Level (LOL)     | 0 V          |            |                |

| Delay (DEL)         | 0 ns         |            |                |

| Output Mode         | Enable       |            |                |

|                     | 20NS         | 3.2V       |                |

| DATA, OUPUT A       |              | 3.2v<br>0v |                |

|                     | <b>→</b> 5NS | 1          | 6510/WF01/7-87 |

Figure 3-34. Pulse Generator Waveform For Glitch Test

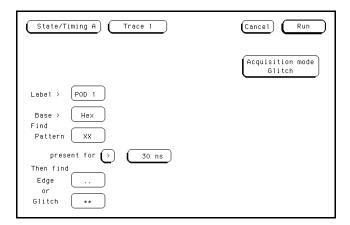

- 3. Assign the pod under test to Analyzer 1 in the Configuration Screen as shown in figure 3-35. Refer to steps *a* and *b* if unfamiliar with menus.

- a. Touch Type field of analyzer 1 and set to Timing.

- b. Touch pod to be tested and assign to Machine 1.

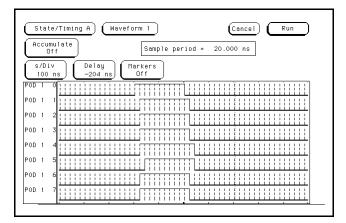

Figure 3-35. Configuration Screen

4. Assign the appropriate eight bits of the pod under test in the Bit Assignment field, then assign the pod to a label in the Format screen as shown in figure 3-36.

Figure 3-36. Format Screen

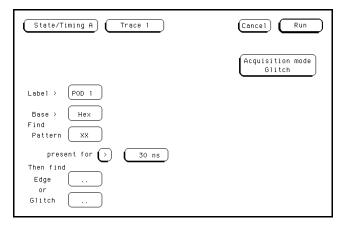

- 5. Configure Trace screen as shown in figure 3-37. Follow steps a through c if unfamiliar with menus.

- a. Set Acquisition mode to Glitch.

- b. Set **Find Pattern** to all DON'T CARE (X's) and **present for** > 30 ns.

- c. Set Then find Glitch on all channels (all \*'s).

Figure 3-37. Trace Screen

6. Touch **Run**, then drag finger to **Single**. The timing analyzer will acquire data and show glitches for channels under test as shown in figure 3-38. Select the Delay field and spin knob to ensure consistent glitch detection.

Figure 3-38. Listing Screen

### **Note**

If sample clock and data synchronize, glitches may be displayed on the Timing screen as valid data transitions.

- 7. Remove pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 3, 4 and 6 until all pods have been tested (pods 1 through 5). Make sure the pod to be tested is assigned in the Configuration screen.

- 8. Disconnect lower eight bits from test connector. Attach upper eight bits to test connector and repeat steps 3, 4, 6 and 7 until the upper eight bits of all pods have been tested (pods 1 through 5).

## 3-15. Threshold Accuracy Test

#### **Description:**

This performance test verifies the threshold accuracy within the three ranges stated in the specification.

#### Specification:

Threshold accuracy: 150 mV accuracy over the range -2.0 to +2.0 volts; 300 mV accuracy over the ranges -9.9 to -2.1 volts and +2.1 to +9.9 volts.

## **Equipment:**

#### Procedure:

1. Connect the HP 16510B and test equipment as shown in figure 3-39.

Figure 3-39. Equipment Setup For Threshold Accuracy

#### **Note**

In this setup, only eight channels are tested at a time to minimize loading. Ground leads must be grounded to ensure accurate test results.

- 2. Assign the pod under test to Analyzer 1 in the Configuration screen as shown in figure 3-35.

- 3. Configure the Format screen for User Defined pod threshold of 0.0 V for the pod under test and assign the appropriate eight bits in the Bit Assignment field as shown in figure 3-40. Refer to steps *a* and *b* if unfamiliar with menus.

- a. Touch the Pod Threshold field, then touch **User defined** and assign appropriate threshold voltage.

- b. Touch the Bit Assignment field and turn on appropriate eight bits to be tested (\* = on; . = off).

Figure 3-40. Format Screen

- 4. Configure Trace screen as shown in figure 3-41. Follow steps a through c if unfamiliar with menus.

- a. Set Acquisition mode to Glitch.

- b. Set **Find Pattern** to all DON'T CARE (x's) and **present for** > 30 ns.

- c. Set **Then find Glitch** to all OFFs (.'s).

Figure 3-41. Trace Screen

- 5. Adjust the power supply output for +150 mV.

- 6. Touch **Run**, then drag finger to **Single**. Data displayed on Waveform screen should be high for the pod under test. See figure 3-42.

Figure 3-42. Waveform Screen

- 7. Adjust power supply for output of -150 mV.

- 8. Touch **Run**. Data displayed on the Waveform screen should be all low for the channels under test as shown in figure 3-43.

Figure 3-43. Waveform Screen

- 9. Return to the Format screen and change User defined Pod Threshold to +9.9 V.

- 10. Adjust power supply for output of +10.2 V.

- 11. Touch **Run**. Data displayed on the Waveform screen should be all high for the pod under test as in previous figure 3-42.

- 12. Adjust power supply for output of +9.6 V.

- 13. Touch Run. Data displayed on the Waveform screen should be all low as in previous figure 3-43.

- 14. Return to the Format screen and change the User defined Pod Threshold to -9.9 V.

- 15. Adjust power supply for output of -9.6 V.

- 16. Touch **Run**. Data displayed in the Waveform screen should be all high for pod under test as in figure 3-42.

- 17. Adjust power supply for output of -10.2 V.

- 18. Touch **Run**. Data displayed in the Waveform screen should be all low for pod under test as in figure 3-43.

- 19. Remove pod body (with probe tip assemblies still connected to test connector) from probe cable of pod under test and connect to probe cable of next pod to test. See figure 3-10. Repeat steps 2 through 18 until all pods have been tested (pods 1 through 5).

- 20. Disconnect lower eight bits from test connector. Attach bits 0 through 7 to test connector and repeat steps 2 through 19 until the upper eight bits of all pods have been tested (pods 1 through 5).

Table 3-1. Performance Test Record

| Hewlett-Packard      |           | Tested By     |

|----------------------|-----------|---------------|

| Model 16510B         |           | Work Order No |

| State/Timing Card    |           | Date Tested   |

| Calibration Interval | 24 Months | Board No      |

| Paragraph Test |                                          | Results |        |        |

|----------------|------------------------------------------|---------|--------|--------|

| 3-7            | Clock, Qualifier, and Data Inputs Test 1 |         | Passed | Failed |

|                |                                          | Pod 1   |        |        |

|                |                                          | Pod 3   |        |        |

|                |                                          | Pod 5   |        |        |

| 3-8            | Clock, Qualifier, and Data Inputs Test 2 |         | Passed | Failed |

|                |                                          | Pod 1   |        |        |

|                |                                          | Pod 2   |        |        |

|                |                                          | Pod 3   |        |        |

|                |                                          | Pod 4   |        |        |

|                |                                          | Pod 5   |        |        |

| 3-9            | Clock, Qualifier, and Data Inputs Test 3 |         | Passed | Failed |

|                |                                          | Pod 2   |        |        |

|                |                                          | Pod 4   |        |        |

| 3-10           | Clock, Qualifier, and Data Inputs Test 4 |         | Passed | Failed |

|                |                                          | Pod 2   |        |        |

|                |                                          | Pod 4   |        |        |

| 3-11           | Clock, Qualifier, and Data Inputs Test 5 |         | Passed | Failed |

|                |                                          | Pod 1   |        |        |

|                |                                          | Pod 2   |        |        |

|                |                                          | Pod 3   |        |        |

|                |                                          | Pod 4   |        |        |

|                |                                          | Pod 5   |        |        |

Table 3-1. Performance Test Record

| Paragraph | Test                                     | Results                                   |        |        |

|-----------|------------------------------------------|-------------------------------------------|--------|--------|

| 3-12      | Clock, Qualifier, and Data Inputs Test 6 | Pod 1<br>Pod 2<br>Pod 3<br>Pod 4<br>Pod 5 | Passed | Failed |

| 3-13      | Clock, Qualifier, and Data Inputs Test 7 | Pod 1<br>Pod 2<br>Pod 3<br>Pod 4<br>Pod 5 | Passed | Failed |

| 3-14      | Glitch Test                              | Pod 1<br>Pod 2<br>Pod 3<br>Pod 4<br>Pod 5 | Passed | Failed |

| 3-15      | Threshold Accuracy Test                  | Pod 1<br>Pod 2<br>Pod 3<br>Pod 4<br>Pod 5 | Passed | Failed |

|           |                                          |                                           |        |        |

# **TABLE OF CONTENTS**

## Adjustments

| 4-1. | Introduction                     | .4-1 |

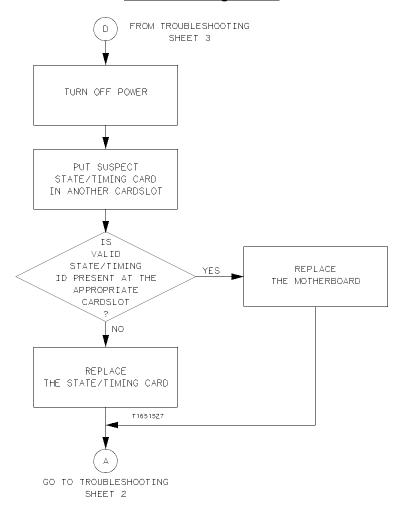

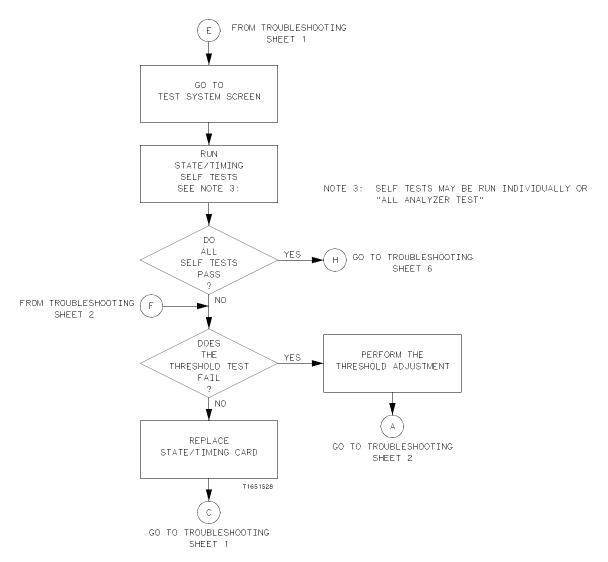

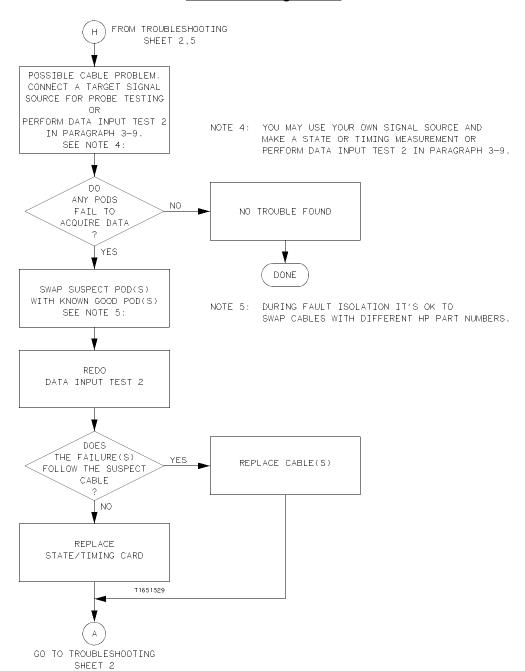

|------|----------------------------------|------|